# Design Platform

Marco Ceccarelli – DG CNECT Matthew Xuereb – DG CNECT

## Design in the semiconductor value chain

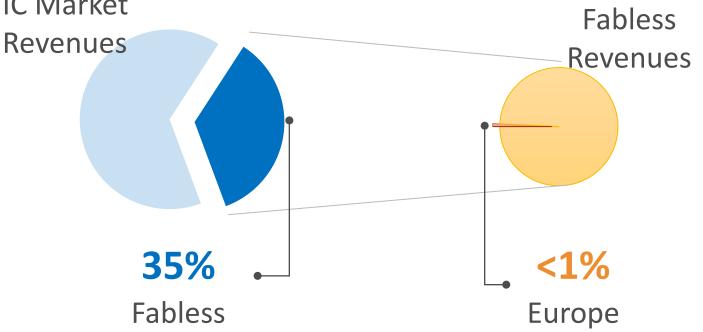

# Europe's fabless problem

4%

10

years

Share of **fabless** declined in

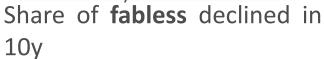

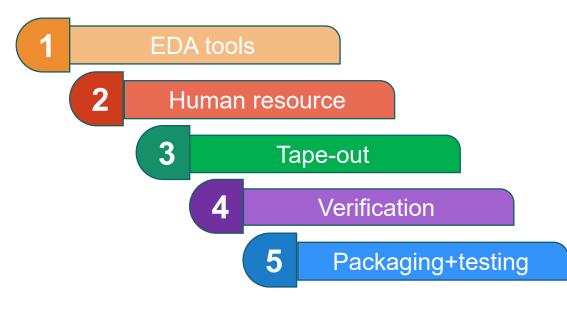

# Challenges for fabless companies

#### Main costs as from user poll:

#### Costs paid to 3rd parties:

- 1. Licensing: EDA, IP, PDK

- 2. Fabrication: MPW, Masks, Package, Test

- 3. IT/infra: CapEx + maintenance, or

GOAL: faster and cheaper design process for SMEs!

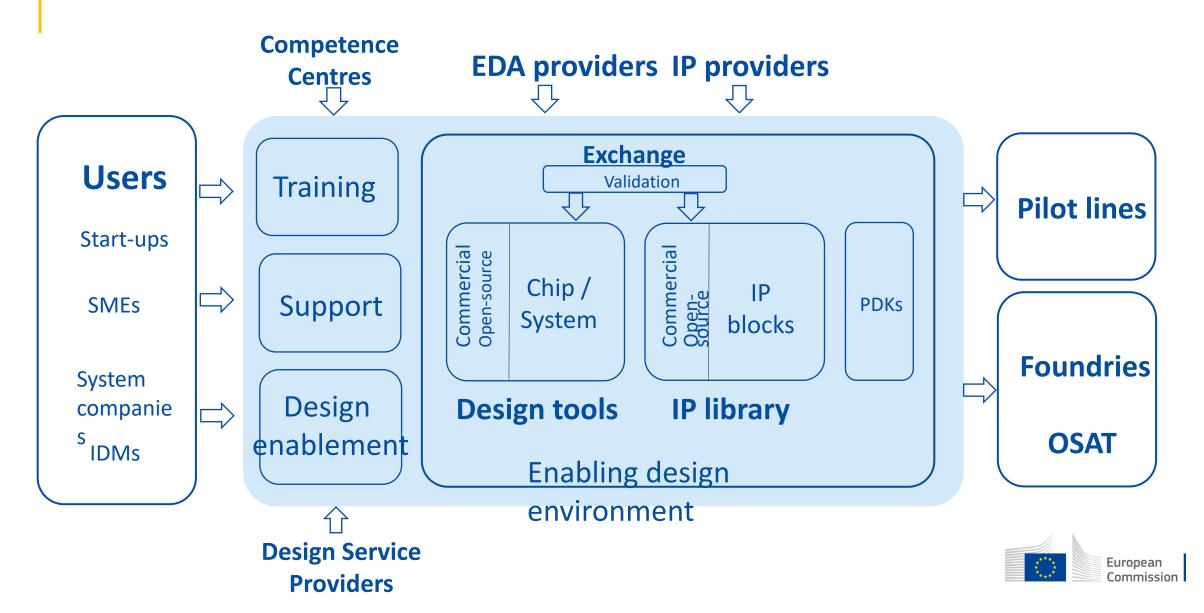

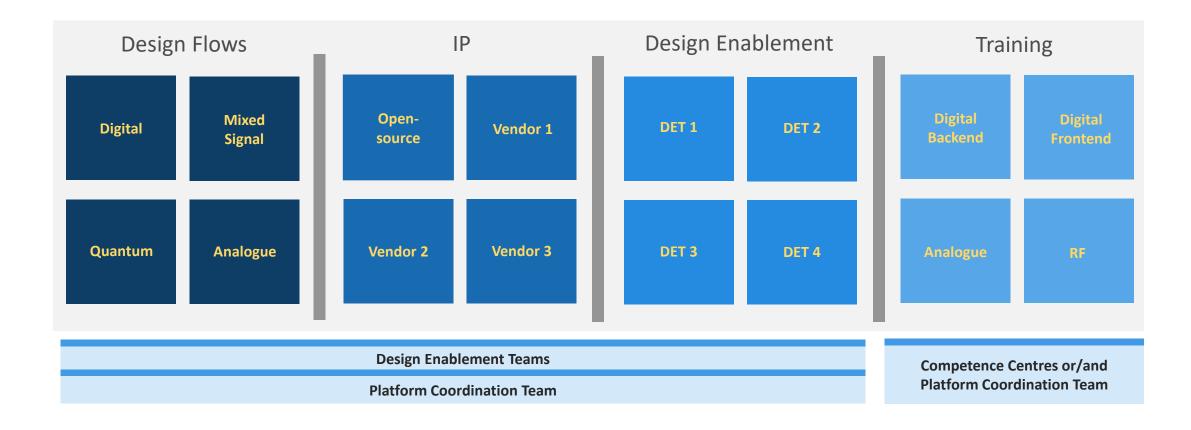

## Design platform - scope

#### **Main objectives**

- Reduce entry barriers and admin burden for EU companies in design

- Facilitate access to pilot lines and foundries

- Foster collaboration among EU stakeholders on new developments

Instrument

ning and support to boost design skills

Develop a virtual design platform, offering cloud-based access to tools, libraries and support services to accelerate development and reduce time-to-market

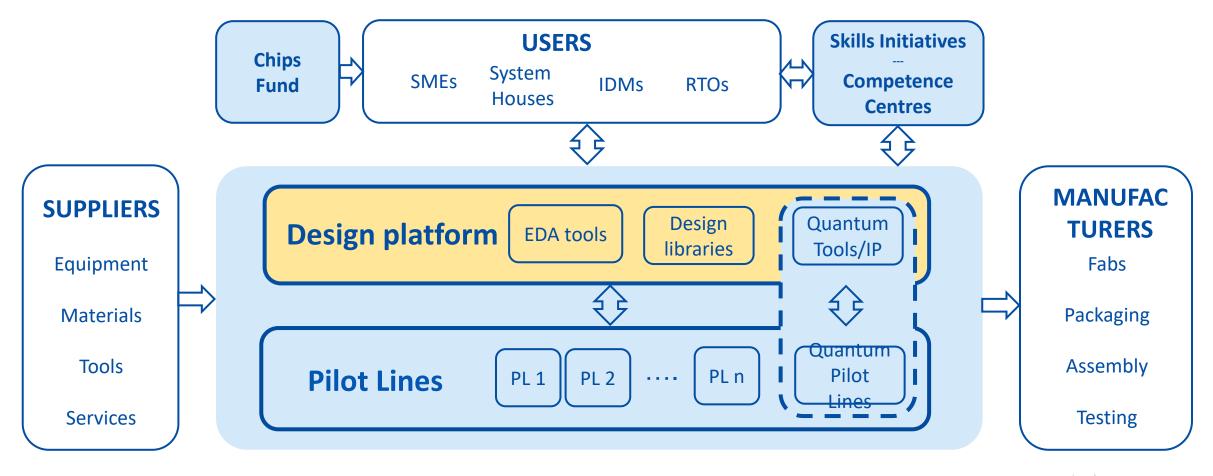

# Chips for Europe Initiative Central role of Design Platform

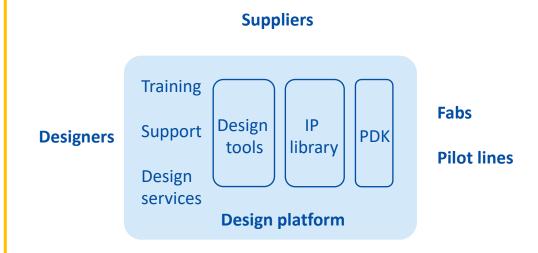

# Design platform

# Design platform – added value

#### **User benefits**

- Easy access to tools and IP in a secure,

scalable cloud environment

- Streamlined licensing process

- Enablement support up to tape-out

- Collaborative spaces for new developments

- Training and support

# Design platform - cloud

#### Why cloud?

No upfront CapEx for on-premise IT

Maximum computing scalability

Growing trend due to increased efficiency and flexibility

AI/ML integration in design: gamechanger

# Design Platform Implementation

#### Design Platform Working Group

SYNOPSYS®

wide coalition of EDA tools & IP vendors, RTOs, IDMs, design houses,

common aim: strengthefingheurope's design ecosystem

#### Design Platform Working Group

Key considerations for implementation

#### Services to be provided by the Design Platform

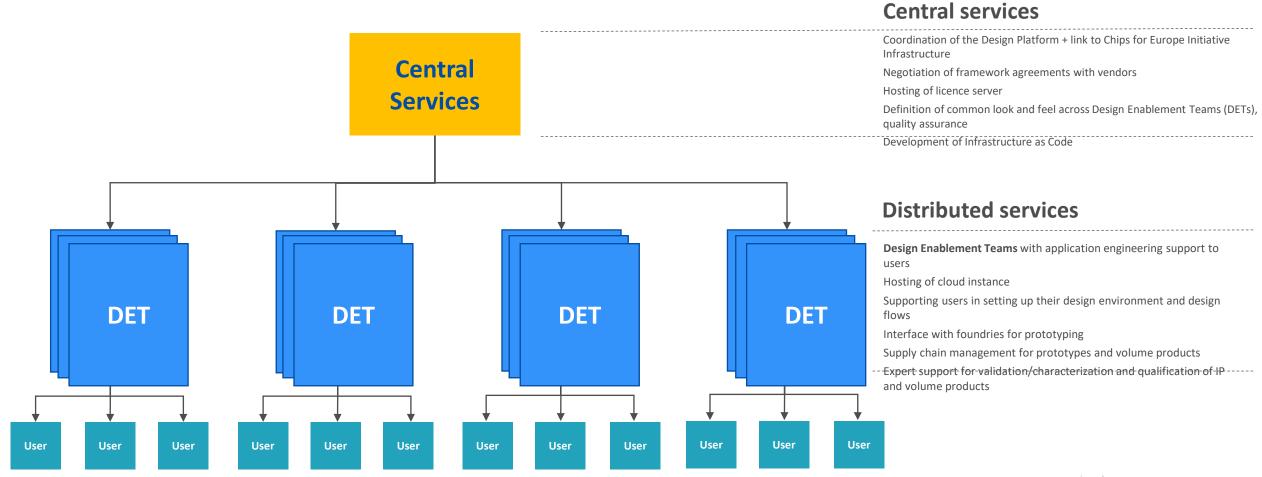

## Finding the right balance...

#### **Centralisation**

Enable aggregation of demand and economies of

#### **Decentralisation**

Allow for customised design environment and expert

support

#### Design Platform Architecture

#### **Cloud Implementation**

**Multi-cloud environment** – the platform will be vendor neutral.

The Platform Coordination Team will be responsible for establishing **framework contracts** with multiple vendors who follow a number of set requirements.

# Enabling users through choice

### Design Platform – Scope of Support

**Application Engineering Support**

# Let's democratise access to chip design in

#### Why go for a Cloud-based solution?

#### Rationale

To provide users with sufficient **scalable** computing resources in an environment that **enables collaboration**. Given the diverse needs of users, the cloud offers a more **flexible** and **efficient** way to manage the entire programme, allowing for seamless adaptation to varying demands (resources, technologies etc.).

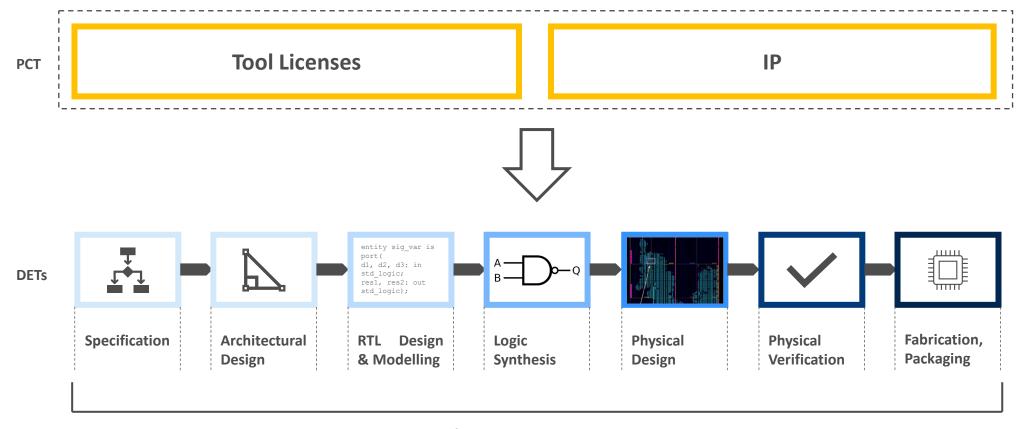

#### Why would a user need a DET?

#### **Application Engineering Support**

Initial setup of design environment and flow configured for a specific foundry technology, related IPs and EDA tools selected by the platform users with appropriate cloud access control and data permissions.

In-project expert support for specific **design flow** tasks to help users in solving blocking issues

Support for project specific EDA tool **issues** (e.g. generation of test cases), or PDK and foundation IP issues

#### **Silicon Flow Support**

Support for **back-end design**, **verification** and **testing**

**Tape-out** handling and **interface with the foundries** (aggregators etc.)

Support for **packaging**, **test**, **validation**, and qualification tasks